## DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING K.S.R. COLLEGE OF ENGINEERING: TIRUCHENGODE – 637 215. COURSE / LESSON PLAN SCHEDULE

## 16EE514 MICROPROCESSORS AND MICROCONTROLLER

## NAME: Mr.E.Kannan

## **CLASS: III-EEE**

## **LEGEND:**

| L  | - Lecture   | PPT | - Power Point      |

|----|-------------|-----|--------------------|

| Т  | - Tutorial  | BB  | - Black Board      |

| Rx | - Reference | 11  | - Pages<br>- Extra |

| Sl.No. | Lecture<br>Hour                                                      | Topics to be covered                                             | Teaching<br>Aid<br>Required | Book No. / Page No.              |

|--------|----------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|----------------------------------|

|        |                                                                      | UNIT I 8085 PROCESSOI                                            | R                           |                                  |

| 1.     | 1.L1Introduction to microprocessor, Hardware<br>Architecture of 8085 |                                                                  | BB & PPT                    | Tx1/pp 34-70<br>Tx1/pp 73-76     |

| 2.     | L2                                                                   | Signals                                                          | BB                          | Tx1/pp 84-86                     |

| 3.     | L3                                                                   | Memory interfacing                                               | BB                          | Tx1/pp 77-80                     |

| 4.     | L4                                                                   | Instruction format, Assembly language format                     | BB                          | Tx1/pp 31-33<br>Tx1/pp 97-102    |

| 5.     | L5, L6                                                               | Instruction set and addressing modes                             | BB                          | Tx1/pp 99-124                    |

| 6.     | L7                                                                   | Assembly language programming                                    | BB                          | Tx1/pp 125-126                   |

| 7.     | L 8                                                                  | Timing Diagram                                                   | BB & PPT                    | Tx1 /pp 87-94                    |

| 8.     | L 9                                                                  | Interrupt structure                                              | BB                          | Tx1/pp 80-83                     |

|        |                                                                      | UNIT II PERIPHERAL INTERF                                        | ACING                       |                                  |

| 9.     | L10                                                                  | Study of Architecture and programming of ICs: 8255 PPI           | BB+PPT                      | Tx1 /pp246-255<br>Rx3/pp 173-211 |

| 10.    | L11                                                                  | 8259 PIC                                                         | BB+PPT                      | Rx3/pp 266-277                   |

| 11.    | L12                                                                  | 8251 USART                                                       | BB+PPT                      | Tx1/pp 281-286<br>Rx3/pp 266-275 |

| 12.    | 12. L13, L14 8279 Key board display controller                       |                                                                  | BB+PPT                      | Tx1/pp 281-294<br>Rx3/pp 235-248 |

| 13.    | L15, L16                                                             | 8253 Timer/ Counter                                              | BB+PPT                      | Tx1/pp 313-321<br>Rx3/pp 224-227 |

| 14.    | L17                                                                  | Interfacing with 8085 - Analog-to-Digital Converter interfacing. | BB+PPT                      | Tx1/pp 345-350<br>Rx3 /pp212-223 |

| 15.    | L18                                                                  | D/A converter interfacing.                                       | BB+PPT                      | Tx1/pp 335-345                   |

|     |          | UNIT III 8051 MICRO CONTRO                                               | OLLER     |                                                      |

|-----|----------|--------------------------------------------------------------------------|-----------|------------------------------------------------------|

| 16. | L 19     | Functional block diagram                                                 | BB+PPT    | Tx1/pp 418-431<br>Tx2/pp 28-32                       |

| 17. | L20      | Data transfer, manipulation instructions                                 |           | Tx1/pp 494-510<br>Tx2 /pp 139-155                    |

| 18. | L21      | Control & I/O instructions, Addressing modes                             | BB        | Tx1/pp 510-518,<br>Tx1/pp 488-493                    |

| 19. | L22, L23 | Timing Diagram                                                           | BB        | Tx1/pp 432-437                                       |

| 20. | L24      | Interrupt structure                                                      | BB        | Tx1/pp 465-470<br>Tx2/pp 317-332                     |

| 21. | L25      | Timer                                                                    | BB        | Tx1/pp 450-456<br>Tx2/ pp 239-255                    |

| 22. | L26      | I/O ports                                                                | BB        | Tx1 /pp438-441<br>Tx2 /pp 94-99                      |

| 23. | L27      | Serial communication                                                     | BB        | Tx1/pp 456-465<br>Tx2 /pp 277-282                    |

|     | UNIT     | IV MICRO CONTROLLER PROGRAMM                                             | ING & APP | LICATIONS                                            |

| 24. | L28, L29 | LCD interfacing                                                          | BB        | Tx2 /pp 352-363                                      |

| 25. | L30, L31 | ADC and DAC interfacing                                                  | BB        | Tx2 /pp 373-402                                      |

| 26. | L32, L33 | Keyboard and display interface                                           | BB        | Tx2 /pp 363-372                                      |

| 27. | L34      | Stepper motor interfacing                                                | BB        | Tx2 /pp 498-506                                      |

| 28. | L35      | Closed loop control of servo motor                                       | BB        | Tx2 /pp 507-517                                      |

| 29. | L36      | DC motor speed control                                                   | BB        | Tx2/pp 507-514                                       |

|     |          | UNIT V ARM PROCESSOR FUNDA                                               | MENTALS   |                                                      |

| 30. | L37      | ARM Core Introduction                                                    | BB        | Rx2 /pp 3-8, 19-21                                   |

| 31. | L38      | Registers, Current Program Status Register                               | BB        | Rx2 /pp 21-29                                        |

| 32. | L39      | Pipeline                                                                 | BB        | Rx2 /pp 29-32                                        |

| 33. | L40      | Exception, Interrupts, Vector Table                                      | BB        | Rx2 /pp 33-34                                        |

| 34. | L41      | Architecture Revisions                                                   | BB        | Rx2 /pp 37-38                                        |

| 35. | L42, L43 | ARM Instruction Set                                                      | BB        | Rx2 /pp 47-84                                        |

| 36. | L44      | Thumb Instruction Set – Thumb Register Usage<br>– ARM-Thumb Interworking | BB        | Rx2 /pp 3-12                                         |

| 37. | L45      | Simple Arithmetic and Logical Programs.                                  | PPT       | soc.csie.ndhu.edu.tw/source/<br>introemb-3/unit1.ppt |

## **TEXT BOOKS**

- A). 1. "Microprocessor and Microcontrollers", Krishna Kant Eastern Company Edition, Prentice Hall ofIndia, New Delhi , 2007.

- 2. Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely "The 8051 Micro Controller and Embedded Systems", PHI Pearson Education, 5th Indian reprint, 2003.

## REFERENCES

- **B)**. 1. R.S. Gaonkar, "Microprocessor Architecture Programming and Application", Wiley Eastern Ltd., New Delhi.

- 2. Andrew N. Sloss, Dominic Symes, Chris Wright, ARM System Developer's Guide, Morgan Kaufmann Series in Computer Architecture and Design, 2004.

- 3. A K Ray, K M Bhurchandi, Advanced Microprocessors and Peripherals, TMH, 2007

## UNIT-1 8085 MICROPROCESSOR(CO1) TWO MARKS

#### 1. What is microprocessor? Give the power supply &clock frequency of 8085.(Remembering)

A microprocessor is a multipurpose, programmable logic device that reads binary instructions from a storage device called memory accepts binary data. As input and processes data according to those instructions and provides result as output. The power of 8085 is +5v and clock frequency in 3MHZ.

#### 2. List the allowed register pairs of 8085. (Remembering)

B-C register pair D-C register pair H-L register pair.

#### 3. Mention the purpose of SID and SOD lines. (Remembering)

SID(serial input data line):It is an input line through which the microprocessor accepts serial data.SOD(serial output data line):It is an output line through which the microprocessor sends output serial data.

#### 4. What is an opcode ? (Remembering)

The part of the instruction that specifies the operation to be performed is called the operation code or opcode.

#### 5. What is the function of IO/M signal in the 8085? (Remembering)

It is a status signal. It is used to differentiate between memory locations and I/O operations when this signal is low (IO/M=0) it denotes the memory related operations. when this signal is high(IO/M=1)it denotes an I/O operation

#### 6. What is meant by wait state? (Remembering)

This state is used by slow peripheral devices. the peripheral devices can transfer the data to or from the microprocessor by using READY input line.the microprocessor remains in the wait state as long as READY line is low. during the wait state, the contents of the address, address/data and control buses are held constant.

#### 7. Explain priority interrupts of 8085?(Understanding)

The 8085 microprocessor has five interrupt inputs.they are TRAP,RST 7.5,RST 6.5,RST 5.5, and INTR.these interrupts have a fixed priority of interrupt service.If two or more interrupts go high at the same time, the 8085 will service them on priority basis.the TRAP has the highest priority followed by RST7.5,RST6.5,RST5.5.the priority of interrupts in 8085 is shown in the table.

| Interrupts | priority |

|------------|----------|

| TRAP       | 1        |

| RST7.5     | 2        |

| RST6.5     | 3        |

| RST5.5     | 4        |

| INTR       | 5        |

## 8. What is the signal classification of 8085? (Remembering)

All the signals of 8085 can be classified into 6 groups

1. Address bus

- 2. Data bus

- 3. Control and status signals 4. Power supply and frequency signals

- 5. Externally initiated signals 6. Serial I/O ports

#### 9. What are the steps involved to fetch a byte in 8085? (Remembering)

i) the pc places the 16-bit memory address on the address busii) the control unit sends the control signal RD to enable the memory chipiii) the byte from the memory location is placed on the data busiv) the byte is placed in the instruction decoder of the microprocessor and the task is carried out according to the instruction.

## **10.** Define instruction cycle, machine cycle and T-state? (Remembering)

Instruction cycle is defined as the time required completing the execution of an instruction.

Machine cycle is defined as the time required completing one operation of accessing memory, I/O or acknowledging an external request.

T –cycle is defined as one subdivision of the operation performed in one clock period.

#### 11. How many machine cycles does 8085 have, mention them? (Remembering)

The 8085 have seven machine cycles they are

- 1. Opcode fetch 2. Memory read

- 3. Memory write 4. I/O read

- 5. I/O write 6. Interrupt acknowledge

- 7. Bus idle

### 12. What are the steps involved to fetch a byte in 8085? (Remembering)

HOLD indicates that a peripheral such a DMA controller is requesting the use of address bus, data bus and control bus.

READY is used to delay the microprocessor read or write cycles until a slow responding peripheral is ready to accept or send data.SID is used to accept serial data bit by bit.

#### **13.Define flags? (Remembering)**

The flags are used to reflect the data conditions in the accumulator.the 8085 flags are ssign flag,zero flag,auxillary flag,parity flag,CY-CARRY FLAG

D7 D6 D5 D4 D3 D2 D1 D0

S Z AC P CY

## 14. Difference between memory mapped I/O and peripheral I/O? (Understanding)

| MEMORY MAPPEED I/O                                                  | PERIPHERAL I/O                                                                      |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 16-bit device address                                               | 8-bit device address                                                                |

| The data transfer between any general-purpose register and I/O port | The data transfer only between accumulator and I/O port                             |

| The memory map(64kb)is shared between I/O device and system memory  | The I/O map is independent of the memory map,256 input device and 256 output device |

| More hardware is required to decode 16-bit address                  | Less hardware is required to decode 8-bit address                                   |

#### **15.** What is an instruction? (Remembering)

An instruction is a binary pattern entered through an input device to command the microprocessor to perform that specific function.

#### **16.** How many operations are there in the instruction set of 8085 microprocessor? (Remembering) There are 74 operations in the 8085 microprocessor

# 17. List out the five categories of the 8085 instructions.give ex of the instructions for each group? (Remembering)

1. Data transfer group – MOV,MVI,LXI

2. Arithmetic group – ADD, SUB, INR.

3. Logical group- ANA,XRA,CMP. 4. Branch group – JMP,JNZ,CALL.

5. Stack I/O and machine control group – PUSH, POP, IN, HLT.

## 18. Explain the difference between a JMP instruction and CALL instruction. (Understanding)

A JMP instruction permanently changes the program counter. A CALL instruction leaves information on the stack so that the original program execution sequence can be resumed.

## 19. Explain the purpose of the I/O instructions IN and OUT(Understanding)

The IN instruction is used to move data from an I/O port in to the accumulator.

The OUT instruction is used to move data from the accumulator to an I/O port.

The IN and OUT instructions are used only on microprocessor, which use a separate address space for interfacing.

#### 20. What is the difference between the shift and rotate instructions? (Understanding)

A rotate instruction is a closed loop instruction. that is, the data moved out at one end is put back in at the other end. the shift instruction loses the data that is moved out of the last bit locations.

# 21. List the four instructions which control the interrupt structure of the 8085 microprocessor? (Remembering)

DI (disable interrupts) EI(enable interrupts) RIM (read interrupt masks) S IM (set interrupt masks)

#### 22. Mention the categories of instruction and give two ex for each category? (Remembering)

The instructions of 8085 can be categorized in to the following five

- 1. Data transfer MOV RD,RS,STA 16-BIT

- 2. Arithmetic ADD R,DCR M.

- 3. Logical XRI 8- bit,RAR

- 4. Branching JNZ CALL 16-bit

- 5. Machine control HLT, NOP

#### 23. Explain LDA, STA AND DAA instructions (Remembering)

LDA copies the data byte in to the accumulator from the memory location specified by the 16bit address.STA copies the data byte from the accumulator in the memory location specified by 16-bit address.DAA changes the content of the accumulator from binary to 4-bit BCD digits.

## 24. Explain the different instruction formats with examples. (Remembering)

The instruction set is grouped in to the following formats

One byte instruction MOV C, A Two byte instruction MVI A, 39H Three byte instruction JMP 2345H

#### 25. What is the use of addressing modes, mention the different types? (Remembering)

The various formats of specifying the operands are called as addressing modes, it is used to access the operands or data. The different types are as follows

1. Immediate addressing 2. Register addressing 3. Direct addressing

4. Indirect addressing 5. Implicit addressing

#### 26. Define stack and stack related instructions? (Remembering)

The stack is a group of memory locations in the R/W memory that is used for the temporary storage of binary information during the execution of the program.the stack related instructions are PUSH and POP

#### 27. Why do we use XRA A instruction? (Understanding)

The XRA A instruction is used to clear the contents of the accumulator and store the value 00H

## 28. How does the microprocessor differentiate b/w data and instruction ? (Understanding)

When the first m/c code of an instruction is fetched and decoded in the instruction register, the microprocessor recognizes the number of bytes required to fetch the entire instruction. for ex MVI A, data, the second byte is always considered as data. if the data byte is omitted by mistake whatever is in that memory location will be considered as data and the byte after the "data" will be treated as the next instruction.

#### 29. What is a recursive procedures? (Remembering)

A recursive procedure is a procedure, which calls itself.recursive procedures are used to work with complex data structures called trees. if the procedure is called with N=3, then the N is decremented by 1 after each procedure CALL and the procedure is called until N=0.

#### 30. How to access subroutine within the main program procedure? (Remembering)

i) accessed by CALL & RET instruction

ii)machine code of instruction is put only once in the memory

iii) with procedures less memory is required

iv)parameters can be passed in registers, memory location or stack

## 31. How clock signals are generated in 8085 and what is the frequency of the internal clock? (Remembering)

The 8085 has the clock generation circuit on the chip but an external quartz crystal or L C circuit or RC circuit should be connected at the pins XI and X2. The maximum internal clock frequency of 8085A is 3.03 MHz.

#### 32. How the microprocessor is synchronized with peripherals? (Remembering)

The timing and control unit synchronizes all the microprocessor operations with clock and generates control signals necessary for communication between the microprocessor and peripherals.

#### 33. What is a bus? (Remembering)

Bus is a group of conducting lines that carries data, address and control signals.

#### 34. Why address bus is unidirectional? (Remembering)

The address is an identification number used by the microprocessor to identify or access a memory location or I/O device. It is an output signal from the processor. Hence the address bus is unidirectional.

#### **35.** What is the function of microprocessor in a system? (Remembering)

The microprocessor is the master in the system, which controls all the activity of the system. It issues address and control signals and fetches the instruction and data from memory. Then it executes the instruction to take appropriate action.

### 36. Why interfacing is needed for 1/0 devices? (Remembering)

Generally I/O devices are slow devices. Therefore the speed of I/O devices does not match with the speed of microprocessor. And so an interface is provided between system bus and I/O devices.

#### 37. What is the difference between CPU bus and system bus? (Remembering)

The CPU bus has multiplexed lines but the system bus has separate lines for each signal. (The multiplexed CPU lines are demultiplexed by the CPU interface circuit to form system bus).

#### **38.** What does memory-mapping mean? (Remembering)

The memory mapping is the process of interfacing memories to microprocessor and allocating addresses to each memory locations.

#### **39.** Why EPROM is mapped at the beginning of memory space in 8085 system? (Remembering)

In 8085 microprocessor, after a reset, the program counter will have OOOOH address. If the monitor program is stored from this address then after a reset, it will be executed automatically. The monitor program is a permanent program and stored in EPROM memory. If EPROM memory is mapped at the beginning of memory space, i.e., at OOOOH, then the monitor program will be executed automatically after a reset.

#### 40. What is the need for system clock and how it is generated in 8085? (Remembering)

The system clock is necessary for synchronizing various internal operations or devices in the microprocessor and to synchronize the microprocessor with other peripherals in the system.

#### 41. What is T -state? (Remembering)

The T-state is the time period of the internal clock signal of the processor. The time taken by the processor to execute the machine cycle is expressed in T-state.

#### 42. What is the need for timing diagram? (Remembering)

The timing diagram provides information regarding the status of various signals, when a machine cycle is executed. The knowledge of timing diagram is essential for system designer to select matched peripheral devices like memories, latches, ports, etc., to form a microprocessor system.

#### 43. Define opcode and operand. (Remembering)

Opcode (Operation code) is the part of an instruction / directive that identifies a specific operation. Operand is a part of an instruction / directive that represents a value on which the instruction acts.

#### 44. What is Vectored and Non- Vectored interrupt? (Remembering)

When an interrupt is accepted, if the processor control branches to a specific address defined by the manufacturer then the interrupt is called vectored interrupt. In Non-vectored interrupt there is no specific address for storing the interrupt service routine. Hence the interrupted device should give the address of the interrupt service routine.

#### 45. List the Software and Hardware interrupts of 8085 ? (Remembering)

Software interrupts : RST 0, RST1, RST 2, RST 3, RST 4, RST 5, RST 6 and RST 7. Hardware interrupts: TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR.

# 46. Write 8085 assembly language instructions to store the contents of the flag register in memory location 2000H.(Understanding)

PUSH PSW POP B MOV A,C STA 2000H. HLT

#### 47. When the 8085 processor accept hardware interrupt? (Remembering)

The processor keeps on checking the interrupt pins at the second T -state of last Machine cycle of every instruction. If the processor finds a valid interrupt signal and if the interrupt is unmasked and enabled then the processor accepts the interrupt. The acceptance of the interrupt is acknowledged by sending an OOA signal to the interrupted device.

## PART B

- 1. Describe the functional pin diagram of 8085. (Remembering) (16)

- 2. Describe the functional block diagram of 8085. (Remembering) (16)

- 3. Explain the 8085 interrupt system in detail. (Remembering) (16)

- 4. Explain various machine cycles supported by 8085. (Remembering) (16)

- 5. Explain the addressing modes of 8085 with example.(understanding) (16)

- 6. Explain the timing diagram of STA instruction. (understanding)

- 7. Draw and explain timing diagram of memory read and memory write machine cycles. (understanding)

- 8. Draw and explain timing diagram of I/O read and I/O write machine cycles. (understanding)

- 9. With neat diagram explain the instruction cycle of LDA instruction. (understanding)

- 10. Explain the Different types of instruction in 8085. (16) (Remembering)

- 11. i) Write a program to arrange /n numbers in ascending order. (8)(apply)

- 12.ii) Write a program to unpack a two digit BCD number stored at memory location 1C00H. (8) (apply)

- 13. Explain the BCD to Decimal code conversion technique and write 8085 assembly language program for the same. (understanding) (16)

- 14. Explain the BCD to Seven Segment code conversion technique and write 8085 assembly language program for the same. (understanding) (16)

- 15. i) Write a program to calculate the factorial of a number between 0 to 8. (apply) (8)

- ii) Write a program to find the number of negative, zero and positive numbers. (apply) (8)

- 16. Explain the following instructions of 8085 and their execution? DAD Rp, DAA, RIM, SIM. (Remembering)

- 17. Draw and explain the timing diagram of IN instruction. (understanding)

- 18. Explain the various conditional call and return instructions in 8085. (Remembering)

- 19. Draw and explain the timing diagram of the DCX instruction. (Remembering)

- 20. List out the sequence of steps to be performed by the microprocessor, when an interrupt occurs. (Remembering)

- 21. Classify the instruction set with respect to data manipulation. (Remembering)

- 22. Draw the timing diagram of MVI A, 3E H. (understanding)

## UNIT-II PERIPHERAL INTERFACING(CO2)

## **TWO MARKS**

#### **1.** What is the use of **8251** chip? (Remembering)

Intel"s 8251A is a universal synchronous asynchronous receiver and transmitter compatible with Intel"s Processors. This may be programmed to operate in any of the serial communication modes built into it. This chip converts the parallel data into a serial stream of bits suitable for serial transmission. It is also able to receive a serial stream of bits and converts it into parallel data bytes to be read by a microprocessor.

#### 2. What are the different types of methods used for data transmission? (Remembering)

The data transmission between points involves unidirectional or bi-directional transmission of meaningful digital data through a medium. There are basically there modes of data transmission

(a)Simplex

(b)Duplex

(c)Half Duplex

In simplex mode, data is transmitted only in one direction over a single communication channel. For example, a computer (CPU) may transmit data for a CRT display unit in this mode.

In duplex mode, data may be transferred between two transreceivers in both directions simultaneously.

In half duplex mode, on the other hand, data transmission may take place in either direction, but at a time may be transmitted only in one direction. For example, a computer may communication with a terminal in this mode. When the terminal sends data (i.e. terminal is sender). The message is received by the computer (i.e. computer is receiver). However, it is not possible to transmit data from the computer to terminal and from terminal to the computer simultaneously.

#### **3.** What is the various programmed data transfer Method? (Remembering)

- i) Synchronous data transfer

- ii) Asynchronous data transfer

- iii) Interrupt driven data transfer

## 4. What is synchronous data transfer? (Remembering)

It is a data method which is used when the I/O device and the microprocessor match in speed. The transfer a data to or from the device, the user program issues a suitable instruction addressing the device. The data transfer is completed at the end of the execution of this instruction.

## 5. What is asynchronous data transfer? (Remembering)

It is a data transfer method which is used when the speed of I/O device does not match with the speed of the microprocessor. Asynchronous data transfer is also called as Handshaking.

## 6. What are the functional types used in control words of 8251a? (Remembering)

The control words of 8251A are divided into two functional types

- 1. Mode Instruction control word

- 2. Command Instruction control word

Mode Instruction control word: - This defines the general operational characteristics of 8251A. Command Instruction control word: - The command instruction controls the actual operations of the selected format like enable transmit/receiver, error reset and modem control.

## 7. What are the basic modes of operation of 8255? (Remembering)

There are two basic modes of operation of 8255, viz.

1. I/O mode. 2. BSR mode

In I/O mode, the 8255 ports work as programmable I/O ports, while in BSR mode only port C (PC0-PC7) can be used to set or reset its individual port bits. Under the IO mode of operation, further there are three modes of operation of 8255, So as to support different types of applications, viz. mode 0, mode 1, and mode 2.

Mode 0- Basic I/O mode

Mode 1-Strobe I/O mode

Mode 2- Strobe bi-direction I/O

## 8. Write the features of mode 0 in 8255? (Remembering)

1. Two 8-bit ports (port A and port B) and two 4-bit ports (port C upper and lower) are available. The two 4-bit ports can be combined used as a third 8-bit port.

2. Any port can be used as an input or output port.

3. Output ports are latched. Input ports are not latched.

4. A maximum of four ports are available so that overall 16 I/O configurations are possible.

## 9. What are the features used mode 1 in 8255? (Remembering)

Two groups A and group B are available for strobe data transfer.

1. Each group contains one 8-bit data I/O port and one 4-bit control/data port.

2. The 8-bit data port can be either used as input or output port. The inputs and outputs both are latched.

3. Out of 8-bit port C, PC0-PC2 is used to generate control signals for port B and PC3=PC5 are used to generate control signals for port A. The inputs PC6, PC7 may be used as independent data lines.

#### **10. What are the signals used in input control signal and output control signals? (Remembering)** Input control signals

| STB (Strobe input)       | IBF (Input buffer full) | INTR (Interrupt request) |

|--------------------------|-------------------------|--------------------------|

| Output control signal    |                         |                          |

| OBF (Output buffer full) | ACK (Acknowledge input) | INTR (Interrupt request) |

## 11. What are the features used mode 2 in 8255? (Remembering)

The signals 8-bit port in group A is available.

- 1. The 8-bit port is bi-directional and additionally a 5-bit control port is available.

- 2. Three I/O lines are available at port C, viz PC2-PC0.

- 3. Inputs and output are both latched.

- 4. The 5-bit control port C (PC3-PC7) is used for generating/accepting handshake Signals for the 8-bit data transfer on port A.

## 12. What are the modes of operation used in 8253? (Remembering)

Each of the three counters of 8253 can be operated in one of the following six modes of operation.

- 1. Mode 0 (Interrupt on terminal count)2. Mode 1 (Programmable monoshot)3. Mode 2 (Rate generator)4. Mode 3 (Square wave generator)5. Mode 4 (Software triggered strobe)6. Mode 5 (Hardware triggered strobe)

- **13. What are the different types of write operations used in 8253? (Remembering)** There are two types write operation in 8253

- (1) Writing a control word register

- (2) Writing a count value into a count register

The control word register accepts data from the data buffer and initialize

- (a) Initializing the operating modes (mode 0- mode 4)

- (b) Selection of counters (counter 0- counter 2)

- (c) Choose binary /BCD counter.

- (d) Loading of the counter registers.

The mode control register is a write only register and the CPU cannot read its contents.

## 14. Give the different types of command words used in 8259A(Remembering)

The command words of 8259A are classified in two groups

1. Initialization command words (ICWs) 2. Operation command words (OCWs)

## **15.** Give the operation modes of **8259A**? (Remembering)

| L                                 | ν <b>υ</b> <sup>μ</sup>       |

|-----------------------------------|-------------------------------|

| (a) Fully Nest Mode               | (b) End of Interrupt          |

| (c) Automatic Rotation            | (d) Automatic EOI mode (e)    |

| Specific Rotation                 | (f) Special Mask Mode         |

| (g) Edge and level Triggered Mode | (h) Reading 8259 Status       |

| (i) Poll command                  | (j) Special Fully Nested Mode |

| (k) Buffered Mode                 | (1) Cascade Mode              |

|                                   |                               |

#### 16. Define scan counter? (Remembering)

The scan counter has two modes to scan the key matrix and refresh the display. In the encoded mode, the counter provides binary count that is to be externally decoded to provide the scan lines for keyboard and display. In the decoded scan mode, the counter internally decodes the least significant 2 bit and provides a decoded 1 out of 4 scan on SL3-SL 3. The keyboard and display both are in the same mode at a time.

### 17. What is the output modes used in 8279? (Remembering)

- 8279 provides two output modes for selecting the display options.

- 1. Display scan

- 2. In this mode, 8279 provides 8 or 16 character- multiplexed displays those can be organized

- as dual 4-bit or single 8-bit display units.

- 3. Display Entry 8279 allows options for data entry on the displays. The display data is entered for display from the right side or from the left side.

## 18. What are the modes used in keyboard modes?(understanding)

- 1. Scanned Keyboard mode with 2 Key Lockout

- 2. Scanned Keyboard with N-Key Rollover.

- 3. Scanned Keyboard Special Error Mode.

- 4. Scanned Matrix Mode.

#### 19. What are the modes used in display modes? (understanding)

- 1. Left Entry Mode

- In the left entry mode, the data is entered from the left side of the display unit.

- 2. Right Entry Mode

In the right entry mode, the first entry to be displayed is entered on the rightmost display.

## 20. What is the use of modem control unit in 8251? (understanding)

The modem control unit handles the modem handshake signals to coordinate the communication between the modem and the USART.

#### 21. List the operation modes of 8255? (Remembering)

a) I/O Mode

i. Mode 0- Simple Input/Output.

ii. Mode 1- Strobe Input/Output (handshake mode)

iii. Mode 2- Strobe bi-directional mode b)

Bit Set/Reset Mode.

#### 22. What is a control word? (Remembering)

It is a word stored in a register (control register) used to control the operation of a program digital device.

#### 23. What is the purpose of control word written to control register in 8255? (understanding)

The control words written to control register specify an I/O function for each I/O port. The bit D7 of the control word determines either the I/O functions of the BSR function.

#### 24. What is the size of ports in 8255? (understanding)

| Port - A | : 8- bits | Port - B | : 8- bits |

|----------|-----------|----------|-----------|

| Port -CU | : 4- bits | Port -CL | : 4- bits |

#### 25. What is an USART? (Remembering)

USART stands for universal Synchronous / Asynchronous Receiver / Transmitter. It is a programmable communication interface that can communicate by using either synchronous or asynchronous serial data.

#### 26. What is the use of 8251 chip? (Remembering)

8251 chip is mainly used as the asynchronous serial interface between the processor and the external equipment.

#### 27. List the major components of the Keyboard/ Display interface. (Remembering)

a. Keyboard section b. Scan section c. Display section d. CPU interface section

## 28. Explain Key bouncing? (understanding)

Mechanical switch are used as keys in most of the keyboard. When a key is pressed the contact bounce back and forth and settle down only after a small time delay (about 20ms). Even though a key is actuated once, it will appear to have been actuated several times. This problem is called Key Bouncing.

#### **29.** What is TXD? (Remembering)

TXD- Transmitter Data Output

This output pin carries serial of the transmitted data bits along with other information like start bit, stop bits and priority bit.

#### 30. Define HRQ? (Remembering)

The hold request output request the access of the system bus. In non- cascaded 8257 systems, this is connected with HOLD pin of CPU. In cascade mode, this pin of a slave is connected with a DRQ input line of the master 8257, while that of the master is connected with HOLD input of the CPU.

## **31. What is RXD? (Remembering)**

RXD- Receive Data Input This input pin of 8251A receives a composite stream of the data to be received by 8251A.

## 32. What are the internal devices of a typical DAC? (Remembering)

The internal devices of a DAC are R/2R resistive network, an internal latch and current to voltage converting amplifier.

## 33. What is setting or conversion time in DAC? (Remembering)

The time taken by the DAC to convert a given digital data to corresponding analog signal is called conversion time.

## 34. What are the different types of ADC? (Remembering)

The different types of ADC are successive approximation ADC, counter type ADC, flash type ADC, integrator converters and voltage to frequency converters.

## 35. Define parallel-to-serial conversion? (Remembering)

In serial transmission, an 8-bit parallel word should be converted in to a stream of eight serial bits. This is known as parallel-to-serial conversion

## 36. Explain serial-to-parallel conversion?(understanding)

In serial reception, the MPU receives a stream of eight bits and it is converted in to 8-bit parallel word. This is known as serial -to- parallel conversion.

## 37. Define Baud? (Remembering)

The rate at which the bits are transmitted is called Baud.

## 38. Write an instruction for serial output data? (Remembering)

MVI A, 80H ;Set D7 in the accumulator = 1 RAR ; Set D6 = 1, SIM.

## 39. List the major components of 8251A programmable communication inteface? (Remembering)

(i)Read/Write control logic, □

(ii)Data register,

(iii)Data bus buffer,

(iii)Control registertransmission receiver

(v)Data bus buffer,

(vi)Modem control

## 40. What is read back command in 8254 timer? (Remembering)

The Read- Back Command in 8254 allows the user to read the count and the status of the counter.

### 41. Give the operating modes of 8259A? (understanding)

- (a) Fully Nested Mode (b) End of Interrupt (EOI) (c) Automatic Rotation

- (d) Automatic EOI Mode (e) Specific Rotation (f) Special Mask Mode

- (g) Edge and level Triggered Mode (h) Reading 8259 Status (i) Poll command

- (j) Special Fully Nested Mode (k) Buffered mode (l) Cascade mode

#### 42. What is the output modes used in 8279? (Remembering)

8279 provides two output modes for selecting the display options.

#### 1. Display Scan

In this mode, 8279 provides 8 or 16 character-multiplexed displays those can be organized as dual 4bit or single 8-bit display units.

#### 2. Display Entry

8279 allows options for data entry on the displays. The display data is entered for display from the right side or from the left side.

## 43. Why ADC and DAC is used in microprocessor based system? (understanding)

More over the development in the microprocessor technology has made it compulsory to process data in the digital form. Since digital system such as microprocessor use a binary system of ones and zero, we have to convert signal from analog form to digital form. The circuits that performs this conversion is called ADC. On the other hand DACs are used when a binary output from a digital system must be converted to some equivalent analog voltage or current.

#### PART B

1. Explain any one of the modes of 8255 in detail. (understanding) (16)

2. With neat block diagram explain PPI. (understanding) (16)

3. i) Using model, write a program to communicate between two microprocessors using 8255. (10) (apply)

ii) Show the control word format of 8255 and explain how each bit is programmed. (6) (apply)

4. With neat block diagram explain the functions of 8259. (Remembering) (16)

5. i) Bring about the features of 8251. (Remembering) (6)

ii) Discuss how 8251 is used for serial communication of data. (understanding) (6)

- iii) Explain the advantages of using the USART chips in microprocessor based systems. (understanding) (4)

- 6. Design an interface circuit needed to connect DIP switch as an input device and display the value of the key pressed using a 7 segment LED display. Using 8085 system, write a program to implement the same. (apply) (16)

- 7. i) Explain the advantages of using the keyboard and display controller chips in microprocessor based system. (understanding) (6)

- ii) Write a program using RST 5.5 interrupt to get an input from keyboard and display it on the display system. (apply) (6)

- iii) Use RST 5.5 instead of RST 7.5 and change mask pattern accordingly. (understanding) (4)

- 8. i) Explain the working of 8254 timer and write a program using it to generate a square waveform of period 3 msec. (apply) (10)

- ii) Describe with any one of the mode configurations of 8254 timer in detail. (understanding) (6)

- 9. Explain how to convert an analog signal into digital signal. (understanding) (16)

- 10. Explain interfacing of ADC with 8085(remembering).

- . 12. Frame the command words ICW1, ICW2, ICW4 AND OCW for initializing single 8259 to initiate INT 40H to INT 47H. The desired features are level triggered interrupt and automatic end of interrupt. (understanding)

- 13. With neat logic schematic of Intel 8279, explain its interfacing with the microprocessor. (remembering)

- 14. Write a program to generate triangular waveform using DAC. (apply)

- 15. With neat diagram explain the interfacing of DAC with 8085. (understanding)

## UNIT-III 8051 MICROCONTROLLERS (CO3) TWO MARKS

#### 1. What is mean by microcontroller?(remembering)

A device which contains the microprocessor with integrated peripherals like memory, serial ports, parallel ports, timer/counter, interrupt controller, data acquisition interfaces like ADC, DAC is called microcontroller.

#### 2. Explain DJNZ instruction of Intel 8051 microcontroller? (understanding)

a) DJNZ Rn, rel

Decrement the content of the register Rn and jump if not zero.

b) DJNZ direct, rel

Decrement the content of direct 8- bit address and jump if not zero.

## **3.** State the function of RS1 and RS0 bits in the flag register of Intel 8051 microcontroller? (understanding) RS1, RS0- Register bank select bits

RS1. RS0- Bank

| ICD I | , KSU- | Dalik  |

|-------|--------|--------|

| 0     | 0      | Bank 0 |

| 0     | 1      | Bank 1 |

| 1     | 0      | Bank 2 |

| 1     | 1      | Bank 3 |

|       |        |        |

## 4. Give the alternate functions for the port pins of port3? (understanding)

RD WR T1 T0

INT 1 INT 0 TXD RXD

RD – Read data control output

WR – Write data control output

$T1-Timer\ /\ counter\ 1\ external\ input\ or\ test\ pin\ T0\ -\ Timer\ /\ counter\ 0\ external$

input or test pin INT 1 – Interrupt 1 input pin

INT 0 – interrupt 0 input pin

TXD - Transmit data pin for serial port in UART mode

RXD – Receive data pin for serial port in UART mode

# 5. Specify the single instruction, which clears the most significant bit of B register of 8051, without affecting the remaining bits. (understanding)

Single instruction, which clears the most significant bit of B register of 8051, without affecting the remaining bits, is CLR B.7.

## 6. Explain the function of the pins PSEN and EA of 8051. (remembering)

PSEN: PSEN stands for program store enable. In 8051 based system in which an external ROM holds the program code, this pin is connected to the OE pin of the ROM.

EA: EA stands for external access. When the EA pin is connected to Vcc, program fetched to address 0000H through 0FFFH are directed to the internal ROM and program fetches to addresses 1000H through FFFFH are directed to external ROM/EPROM. When the EA pin is grounded, all addresses fetched by program are directed to the external ROM/EPROM.

# 7. Explain the 16-bit registers DPTR and SP of 8051. (understanding) DPTR:

DPTR stands for data pointer. DPTR consists of a high byte (DPH) and a low byte (DPL). Its function is to hold a 16-bit address. It may be manipulated as a 16- bit data registers. It serves as a base register in indirect jumps, lookup table instructions and external data transfer.

## SP:

SP stands for stack pointer. SP is a 8-bit wide register. It is incremented before data is stored during PUSH and CALL instructions. The stack array can reside anywhere in-chip RAM. The stack pointer is initialised to 07H after a reset. This causes the stack to begin at location. 08H.

## 8. Name the special functions registers available in 8051. (remembering)

| Accumulator       | B Register P       | rogram statı | us Word. Stack pointer.    |

|-------------------|--------------------|--------------|----------------------------|

| Data pointer      |                    |              |                            |

| Port 0            | Port 1             | Port 2       | Port 3                     |

| Interrupt priorit | y control register | Interrup     | t enable control register. |

## 9. Explain the register IE format of 8051. (understanding)

EA ET2 ES ET1 EX1 ET0 EX0 EA- Enable all control bit. ET2- Timer 2 interrupt enable bit. ES- Enable serial port control bit. ET1- Enable Timer1 control bit. EX1-Enable external interrupt1 control bit. ET0-Enable Timer0 control bit. EX0-Enable external interrupt0 control bit.

#### 10. Compare Microprocessor and Microcontroller. (understanding) Microprocessor Microcontroller

Microprocessor 1. Microprocessor contains ALU, general register counter, clock timing

2. It has many instructions to move data etween memory and CPU.

3. It has one or two bit handling instruction .

interrupt circuit.

- 4. Access times for memory and I/O Devices are more.

- 5. Microprocessor based system requires more hardware

Microcontroller contains the circuitry of Purpose microprocessor and in addition it has Circuit and Built-in ROM, RAM, I/O devices and Counter

It has many instructions to move data between memory and CPU. It has many bit handling instructions.

Less access times for built-in memory and I/O devices. Microcontroller based system requires less hardware reducing PCB size and Increasing the reliability.

#### 11. Name the five interrupt sources of 8051? (remembering)

| The interrupt are:           | Vector address |

|------------------------------|----------------|

| External interrupt 0: IE0:   | 0003H          |

| Timers interrupt 0: TF0:     | 000BH          |

| External interrupt 1: IE1:   | 0013H          |

| Timers interrupt 1: TF1:     | 001BH          |

| Serial interrupt             |                |

| Receive interrupt: RI:       | 0023H          |

| Transmit interrupt: TI: 0023 | 3H             |

|                              |                |

# **12.** Write a program to subtract the contents of **RI** of Bank0 from the contents of **R0** 0f Bank2. (apply)

MOV PSW, #10 MOV A, R0 MOV PSW, #00 SUBB A, R1

## 13. How the RS-232 serial bus is interrupt to 1TL logic device? (understanding)

The RS-232 signal voltage level devices are not compatible with TTL logic levels. Hence for interfacing TTL devices to RS-232 serial bus, level converters are used. The popularly used level converters are MC 1488 & MC 1489 or MAX 232.

#### 14. List some of the features of 8096 microcontroller. (remembering)

a. The 8096 is a 16-bit microcontroller.

b. the 8096 is designed to use in application which require high speed calculations and fast I/O operation.

c. The high speed I/O section of an 8096 includes a 16-bit timer, a 16- bit counter, a 4 input programmable edge detector, 4 software timer and counter 6-output programmable events Generator.

d. It has 100 instructions, which can operate on bit, byte, word and double words.

e. The bit operation is possible and these can be performed on any bit in the register file or in the special function register.

## 15. List the features of 8051 microcontroller? (remembering)

The features are

- Single supply +5 volt operation using HMOS technology.

- 4096 bytes program memory on chip (not on 8031)

- 128 data register banks

- Four register mode, 16-bit timer/ counter.

- Extensive Boolean processing capabilities.

- 64 KB external RAM size

- 32 bi-directional individually addressable I/Olines.

- 8 bit CPU optimized for control applications.

## 16. Explain the operating mode 0 of 8051 serial ports?(understanding)

In this mode serial enters & exits through RXD, TXD outputs the shift clock 8 bits are transmitted/received: 8 data bits (LSB first). The baud rate is fixed at 1/12 the oscillator frequency.

## 17. Explain the operating mode 1 of 8051 ports? (understanding)

In this mode 11 bits are transmitted (through TXD) or received (through RXD): a start bit (0),

8 data bits (LSB first) a, programmable 9<sup>th</sup> data bit, & a stop bit (1).ON transmit the 9<sup>th</sup> data bit (TB\* in SCON) can be assigned the value of 0 or 1.

For eg: the parity bit (P, in the PSW) could be moved into TB8. On receive the 9<sup>th</sup> data bit go in to the RS8 in Special Function Register SCON, while the stop bit is ignored. The baud rate is programmable to either 1/32, or 1/64 the oscillator frequency.

## 18. Explain the mode 3 of 8051 serial ports? (understanding)

In this mode 11 bits are transmitted (through TXD) or received (through RXD): a start bit (0),

8 data bits (LSB first) a, programmable 9<sup>th</sup> data bit, & a stop bit (1). In fact, Mode 3 is the same as Mode 2 in all respect except the baud rate. The baud rate in Mode 3 is variable.

In all the four modes, transmission is initiated by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI=0 & REN=1. Reception is initiated in other modes by the incoming start bit if REn=1.

## 19. List the addressing modes of 8051? (understanding)

Direct addressing, Register addressing, Register indirect addressing, Implicit addressing Immediate addressing, Index addressing, Bit addressing

## 20. Give the format of PSW register of 8051. (remembering)

| CY | AC  | FO | RS1 | RS0 | OV | - | Р |

|----|-----|----|-----|-----|----|---|---|

| ~  | ~ ~ | ~  |     |     |    |   |   |

| CY – Carry flag                  |

|----------------------------------|

| AC – Auxiliary carry flag        |

| F0 – User flag 0                 |

| RS1 – Register bank select bit 1 |

| RS0: Register bank select bit 0  |

OV: Overflow flag

P: Parity flag. 1 – Odd parity

## 21. What is the use of PCON register? (remembering)

The power mode control (PCON) special function register in the serial data input / output transmission, controls the data rates.

## 22. What is the use of SCON register? (remembering)

The serial port control (SCON) special function register in the serial data input / output transmission is used to controls data communication.

## 23. What is the use of TCON register? (remembering)

All the counter action is controlled by bit states in the timer / counter control register (TCON) and certain program instructions.

#### 24. What is the bit pattern of IP in 8051 microcontroller? (remembering)

| - | - | PT2 | PS | PT1 | PX1 | PT0 | PX0 |

|---|---|-----|----|-----|-----|-----|-----|

|---|---|-----|----|-----|-----|-----|-----|

PT2 – Reserved for future use.

PS – Priority of serial port interrupts. Set / cleared by program.

PT1 – Priority of timer 1 overflow interrupt. Set / cleared by program.

PX1 – Priority of external interrupt 1. Set / cleared by program.

PT0 – Priority of timer 0 overflow interrupt. Set / cleared by program.

PX0 – Priority of external interrupt 0. Set / cleared by program.

## 25. What is the significant of GATE bit in TMOD control register? (remembering)

OR gate enable bit which controls RUN / STOP of timer 1/0. Set to 1 by program to enable timer to run if bit TR1/0 in TCON is set and signal on external interrupt INT 1/0 pin is high. Cleared to 0 by program to enable timer to run if bit TR1/0 in TCON is set.

## 26. What is the bit pattern of IE in 8051 microcontroller? (remembering)

|                                                                            | EA | - | ET2   | ES                                       | ET1          | EX1     | ET0 | EX0 |  |

|----------------------------------------------------------------------------|----|---|-------|------------------------------------------|--------------|---------|-----|-----|--|

| EA – Enable interrupt bits. ET2                                            |    |   |       | – Reserve                                | ed for futur | re use. |     |     |  |

| ES – Enable serial port interrupt.                                         |    |   | rupt. | ET1 – Enable timer 1 overflow interrupt. |              |         |     |     |  |

| EX1 – Enable external interrupt 1 ET0 – Enable timer 0 overflow interrupt. |    |   |       |                                          | rrupt.       |         |     |     |  |

EX0 – Enable external interrupt 0.

#### 27. What is the Interrupt Priority given in 8051 microcontroller? (remembering)

IE0 - 0003HTFO - 000BHIE1 – 0013H TF1 - 001BHSERIAL = RI OR TI - 0023H

## 28. What is the SFR address of TMOD, TCON, TL0, TH1, P0, SBUF? (remembering)

TMOD – 89H TCON – 88H TL0 – 8AH TH1 –8DH P0 –80H SBUF – 99H

## 29. Explain the MUL AB and DIV AB of 8051 microcontroller instructions.(understanding)

MUL AB – multiply the A and B register contents and place the 16-bit result in B and A.i.e., t he lower byte is in A and upper byte is in B.

DIV AB – divide A and B. In dividing a byte by byte, the numerator must be in register A and the denominator must be in B. After the DIV instruction is performed, the quotient is in A and the remainder is in B.

#### 30. Write a program to perform multiplication of 2 numbers using 8051. (apply)

MOV A,#data 1 MOV B,#data 2 MUL AB MOV DPTR,#5000 MOV @DPTR,A(lower value) INC DPTR MOV A,B MOVX @ DPTR,A

## 31. Write a program to mask the 0th &7th bit using 8051? (apply)

MOV A,#data ANL A,#81 MOV DPTR,#4500 MOVX @DPTR,A LOOP SJMP LOOP

## 32. Write about CALL statement in 8051?( remembering)

There are two subroutine CALL instructions. They are \*LCALL (Long CALL) and \*ACALL (Absolute CALL). Each increments the PC to the 1st byte of the instruction & pushes them in to the stack.

## 33. Write about the jump statement?

There are three forms of jump. They are **LJMP** (Long jump)-address 16, **AJMP** (Absolute Jump)-address 11 and **SJMP** (Short Jump)-relative address.

## 34. Write program to load accumulator, DPH, & DPL using 8051? (apply)

MOV A,#30 MOV DPH,A MOV DPL,A

## **35. Write a program to add 2 8-bit numbers using 8051? (apply)** MOV A,#30H ADD A,#50H

## 36. What is the role of SWAP instruction available in 8051? (remembering)

MOV A, #12H : The immediate data 12 available in Accumulator. SWAP A : 21 is available in Accumulator.

- **37. Write a program to subtract 2 8-bit numbers &exchange the digits using 8051? (apply)** MOV A,#9F MOV R0,#40 SUBB A,R0 SWAP A

- 38. Write a program using 8051 assembly language to change the date 55H stored in the lower byte of the data pointer register to AAH using rotate instruction. (apply)

MOV DPL,#55H MOV A, DPL RL A label :SJMP label

**39.** Explain the contents of the accumulator after the execution of the following program

```

segments: (apply)

```

MOV A,#3CH MOV R4,#66H ANL A,R4 A 3C R4 66 Ans : A = 24

- **40.** Write a program to load accumulator A, DPH and DPL with 30H. (apply) 1) MOV A,#30 2)MOV DPH,A 3)MOV DPL,A

- 41. Mention the advantage of register indirect addressing mode. ( remembering)

It makes accessing data dynamic rather than static as in case of direct addressing mode.

42. What is the limitation of register indirect addressing mode in 8051 microcontroller? (remembering)

R0 and R1 are the only registers that can be used for pointers in register indirect addressing mode. Since R0 and R1 are 8-bit wide, their use is limited to accessing any information in the internal RAM (scratch pad memory).

## 43. Write a program to clear 16 RAM locations starting at RAM address 60H. (apply)

| CLR  | А                        |

|------|--------------------------|

| MOV  | R1, #60H                 |

| MOV  | R7, #16                  |

| MOV  | @R1, A                   |

| INC  | R1                       |

| DJNZ | R7, AGAIN                |

|      | MOV<br>MOV<br>MOV<br>INC |

# 44. Write a program to copy a block of 10 bytes of data from RAM locations starting at 35H to RAM locations starting at 60H. ((apply)

|       | MOV  | R0, #35H   |

|-------|------|------------|

|       | MOV  | R1, #60H   |

|       | MOV  | R3, #10    |

| BACK: | MOV  | A, @R0     |

|       | MOV  | @R1, A     |

|       | INC  | <b>R</b> 0 |

|       | INC  | R1         |

|       | DJNZ | R3, BACK   |

## PART-B

- 1. Describe the architecture of 8051 with neat diagram. (16)

- 2. i) Discuss the peripheral interface of 8051.(8) (Remembering)

ii) Explain the interrupt structure of 8051 microcontroller Explain how interrupts are prioritized. (understanding)

- 3. i) What is the difference between the Microprocessors and Microcontrollers?(8)(understanding)ii) Explain the I/O port structure of 8051. (8) (understanding)

- 4. i) Explain the different serial communication modes in 8051. (8) (Remembering)ii) Explain the memory structure of 8051. (8) (Remembering)

- 5. Explain the functional pin diagram of 8051 Microcontroller. (16) (Remembering)

- 6. Explain the timer, couter operation using 8051. (understanding)

- 7. Explain the timer modes of operation of 8051. (Remembering)

- 8. (a).Explain how the memory is organized in 8051 family of controller.(b).What are the functional blocks available in 8051? Explain with a block diagram. (Remembering)

- 9. (a) How does the timer operate in 8051 in mode 2? Explain with suitable diagram.

(b)Assuming XTAL = 11.0592 MHz, write a 8051 assembly language program to generate a square wave of 50 Hz frequency on pin P 2.3. (apply)

- 10. Explain how serial data communication is achieved in 8051 microcontroller? (understanding)

- 11. Explain internal RAM organization of 8051. (Remembering)

- 12. Explain TCON, SCON & TMOD SFRs of 8051. (understanding)

- 13. Explain the polling mechanism to select an interrupt among the pending interrupts in 8051. Give steps to program 8051 for serial data transfer. (apply)

- 14. Write the vector address and priority sequence of 8051 interrupts. (Remembering)

- 15. Write a delay routine for 1 millisecond using timer 0 of 8051 for 12 MHz crystal frequency. . (apply)

- 16. i) How do you calculate baud rate for serial communication for 8051? . (understanding)

- ii) What is the function of SM2 bit present in the scon register in 8051? . (understanding)

- 17. a) Calculate the reload value of timer 1 for achieving a baud rate of 4800 in 8051 for a crystal frequency of 11.0592 M Hz. . (understanding)

- b) Write short description on register bank registers and their uses. (Remembering)

- 18. Explain the following instructions of 8051 with examples. (Remembering)i) CJNE destination, source, label ii) MUL AB, iii) RRL A, iv) SWAP A, v) SETB P2.0

- 19. Explain the following instructions of 8051: (Remembering)

- i) MOV @R1,#05H, ii) XRL 15H, # 88H, iii) MOVX A, @DPTR, iv) SUBB A, # 20H,

- v) XCH A, R7

- 20. Write a program to find a number that when XOR ed to the A register, results in the number 3FH in A. (apply)

- Write a program to copy the bytes stored at 0100H to 0102H to internal RAM locations 20H to 22H. (apply)

## UNIT IV MICRO CONTROLLER APPLICATIONS(CO4)

## **TWO MARKS**

- 1. Write an 8051 assembly language simple program to control stepper motor. (Apply) START : MOV DI, 1200H MOV CX, 0004H LOOP 1 : MOV AL,[DI] OUT 0C0,AL MOV DX, 1010H L1 : DEC DX JNZ L1 INC DI LOOP LOOP1 JMP START 1200 : 09,05,06,0A

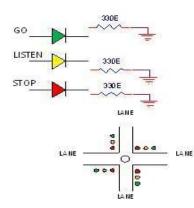

- 2. Draw the diagram of traffic light control.(remembering)

Make high to - LED On

Make low to - LED Off

## 3. Write a program for pulse width measurement. (Apply)

| Lable | Instruction    |

|-------|----------------|

|       | MOV TMOD, #09  |

| MAIN  | MOV TL0, #00   |

|       | MOV TH0, #00   |

| LOOP1 | JB P3.3, LOOP1 |

| LOOP2 | JNB P3.3 LOOP2 |

|       | SETB TR0       |

| LOOP3 | JB P3.3, LOOP3 |

|       | CLR TR0        |

|       | MOV R6, TL0    |

|       | MOV R7, TH0    |

|       | LCALL 675F     |

|       | SJMP MAIN      |

## 1. What is the EOI? (remembering)

#### **End of Interrupt(EOI)**

The ISR bit can be reset by an End og Interrupt command issued by the MPU, usually just before exiting from the interrupt routine.

In the Fully Nested Mode, the highest level in the ISR would necessarily correspond to the last interrupt acknowledged and serviced. In such a case, a non-specific EOI command may be issued by the MPU.

However, if an FNM is not used, the 8259 may not be able to determine the last interrupt acknowledged. In such a case, a specific EOI command will have to be issued by the MPU.

It should be noted that in the cascade mode, the EOI command must be issued twice, once for the master and once for the slave.

## 2. What is meant by full step sequence? (remembering)

In the full step sequence, two coils are energized at the same time and motor shaft rotates. The order in which coils has to be energized is given in the table below.

| Full Mode Sequence |   |   |               |                       |

|--------------------|---|---|---------------|-----------------------|

| Step               | А | В | $A \setminus$ | $\mathbf{B}\setminus$ |

| 0                  | 1 | 1 | 0             | 0                     |

| 1                  | 0 | 1 | 1             | 0                     |

| 2                  | 0 | 0 | 1             | 1                     |

| 3                  | 1 | 0 | 0             | 1                     |

## 3. What is the use of solid state relays? (remembering)

A solid-state relay (SSR) is an electronic switching device in which a small control signal controls a larger load current or voltage. It consists of a sensor which responds to an appropriate input (control signal), a solid-state electronic switching device which switches power to the load circuitry, and some coupling mechanism to enable the control signal to activate this switch without mechanical parts. The relay may be designed to switch either AC or DC to the load.

#### 4. What is the advantage of opto- isolator? (remembering)

In <u>electronics</u>, an opto-isolator, also called an optocoupler, photocoupler, or optical isolator, is a component that transfers electrical signals between two isolated circuits by using light. Opto-isolators prevent <u>high voltages</u> from affecting the system receiving the signal. Commercially available opto-isolators withstand input-to-output voltages up to 10 kV and voltage transients with speeds up to  $10 \text{ kV}/\mu s$ . A common type of opto-isolator consists of an <u>LED</u> and a <u>phototransistor</u> in the same package. Opto-isolators are usually used for transmission of digital (on/off) signals, but some techniques allow use with analog (proportional) signals.

## 5. What is meant by stepper motor? (remembering)

A stepper motor (or <u>step</u> motor) is a <u>brushless DC electric motor</u> that divides a full rotation into a number of equal steps. The motor's position can then be commanded to move and hold at one of these steps without any feedback sensor (an <u>open-loop controller</u>), as long as the motor is carefully sized to the application.

## 6. How PWM used in the speed control of DC motor? (understanding)

A pulse width modulator (PWM) is a device that may be used as an efficient light dimmer or DC motor speed controller. The circuit described here is for a general purpose device that can control DC devices which draw up to a few amps of current. The circuit may be used in either 12 or 24 Volt systems with only a few minor wiring changes. This device has been used to control the brightness of an automotive tail lamp and as a motor speed control for small DC fans of the type used in computer power supplies.

## 7. What are the tasks involved in keyboard interfacing? (remembering)

The task involved in keyboard interfacing are sensing a keyboard interfacing are sensing a key actuation, de bouncing the key and generating key codes(decoding the key).these task are performed software if the keyboard is interfaced through ports and they are performed by hardware if the keyboard is interfaced through 8279.

## 8. How a keyboard matrix is formed in keyboard interface ? (understanding)

The return lines RL0 to RL7 of 8279 are used to form the columns of keyboard matrix.in decoded scan the scan lines SLO to SL3 of 8279 are used to form the rows of keyboard matrix. In encoded scan mode, the output lines of external decoder are used as rows of keyboard matrix.

#### 9. What is scanning in keyboard and what is scantime? (remembering)

The process of sending a zero to each row of a keyboard matrix and reading the columns for key actuation is called scanning. the scan time is the time taken by the processor to scan all the rows one by one starting from first row and coming back to the first row.

## **10.** What is scanning in display and what is the scan time? (remembering)

In display devices the process of sending display codes to 7-segment LED"S to display the led"s one by one is called scanning. The scan time is the time taken to display all the 7- segment LED"S one by one, starting from first LED and coming back to the first LED again.

#### 11. Give some ex of input devices to microprocessor-based systems(remembering)

The input devices used in the microprocessor- based system are keyboards, DIP switches, ADC, floppy disc, etc.

#### PART-B

1. i) Write 8051 ALP to read data from port I when negative edge triggered at INTO and supply the data to port 2 by masking the upper 4 bits. (8) (Apply)

ii) Write 8051 ALP to transmit "Hello World" to PC at 9600 baud for external crystal frequency of 11.0592MHz. (8) (Apply)

- 2. With a neat circuit diagram explain how a 4 x 4 keypad is interfaced with 8051 microcontroller and write 8051 ALP for keypad scanning. (16) (Apply)

- 3. Draw the schematic for interfacing a stepper motor with 8051 microcontroller and write ALP for changing speed and direction of motor. (16) (Apply)

- 4. Draw the schematic for interfacing a servo motor with 8051 microcontroller and write

ALP for servo motor control. (16) (Apply)

- 5. Develop a program for 8 bit multiplication and division using 8051 microcontroller Instruction set. (Apply)

- 6. Develop a program for 8 bit addition and subtraction using 8051 microcontroller instruction set. (Apply)

- 7. i) Write a 8051 ALP to find Fibonacci series of N given numbers. (8) (Apply)ii) Write a 8051 ALP to find the average of given N numbers. (8) (Apply)

- 8. Draw the schematic for interfacing a DC motor with 8051 microcontroller and write 8051 ALP for changing speed and direction of motor. (16) (Apply)

- 9. Explain the interface LCD module with 8051 microcontroller and write ALP(16) (Apply)

- 10. With neat diagram explain the interfacing of ADC with 8051.(remembering)

- 11. With neat diagram explain the interfacing of DAC with 8051. (remembering)

## UNIT V

#### **ARM PROCESSOR FUNDAMENTALS(CO5)**

#### **TWO MARKS**

## 1. Define Pipelining. (remembering)

Starting the execution of next instruction before the current instruction execution is finished with the available hardware resources is called pipelining. This is achieved by splitting the execution of each instruction for more than one stage and allocating appropriate hardware for each stage. To improve the utilization of hardware resources, and also the processor throughput, pipelining organization is implemented.

### 2. What are the sequences of steps in pipelining? (remembering)

- A typical pipelining sequence may be as follows:

- •Fetch fetch instruction from memory.

- •Decode generating control signals for that instruction.

- •Register accessing any operands from register.

- •ALU-combine the operands to produce results or memory address.

- •Memory–access memory for a data operand.

- •Result write the result back to the register bank.

#### 3. What are the hazards occur in pipelining? (remembering)

Read-after-write pipeline hazard – occurs when an instruction waits for an operand which is the result of the previous instruction. Branching hazards – since branch instructions modify the flow of program, it flush and refill the pipeline.

#### 4. List the features of RISC architecture. (remembering)

•Fixed 32-bit instruction size with predefined formats.

- •Load store architecture.

- •Large register bank of 32–bit registers.

#### 5. List the features of RISC processor. (remembering)

- •Hardwired decode logic.

- •Pipelined execution.

- •Single cycle execution.

#### 6. Mention the advantages and drawbacks of RISC. (remembering)

Advantages: • Smaller diesize. • Shorter development time. • Higherperformance. • Higher clock rate with single cycle execution. Drawbacks: • RISCs generally have poor code density. • RISCs don''t execute x86 code.

## 7. How higher clock rates are achieved in RISC? (remembering)

Higher clock rates is achieved by,Single cycle execution.High memory access rate.

8. What are the factors to be considered for low power circuit design? (remembering)

Minimize the power supply voltage, Vdd.

Minimize the circuit activity, A.

Minimize the number of gates.

Minimize the clock frequency.

## 9. Mention the features of RISC which are used and rejected in ARM processors.

## (remembering)

#### **Features used:**

- 1. Load store architecture

- 2. 2. Fixed-length 32-bit instructions.

- 3. 3-address instruction formats.

### **Features rejected:**

- 1. Register windows

- 2. Delayed branches

- 3. Single cycle execution of all instructions.

## 10. Explain the ARM CPSR format. (remembering)

CPSR-Current Program Status Register is used to store the status bits.

| 31   | 28 27  | 8 | 7 6 | 5 4 | 4    | 0 |

|------|--------|---|-----|-----|------|---|

| NZCV | unused |   | ΙF  | Т   | mode |   |

•Mode [4:0] (lower 5 bits) – represents the processor operating mode.

•T  $- 5^{\text{th}}$  bit: represents currently ARM or Thumb instruction is executed.

•I,  $F - 6^{th}$ , 7th bits: interrupt flag and fast interrupt flag.

•N, Z, C, V –Negative, Zero, Carry, overflow flags.

## 11. How data items are arranged in memory system? (understanding)

Memory may be viewed as a linear array of bytes numbered from zero up to2^32-1. Data items may be 8bit bytes, 16-bit half-words or 32-bit words. A word-sized data item must occupy a group of four byte locations starting at a byte address which is a multiple of four. Half-words occupy two byte locations starting at an even byte address.

#### 12. Define Load-store architecture. (remembering)

This means that the instruction set will only process (add, subtract, and soon) values which are in registers (or specified directly within the instruction itself), and will always place the results of such processing into a register. The only operations which apply to memory state are ones which copy memory values into registers (Load instructions) or copy register values into memory (store instructions).

#### 13. List the types of ARM instructions. (remembering)

All ARM instructions fall into one of the following three categories:

- 1. Data processing instructions.

- 2. Data transfer instructions.

- 3. Control flow instructions.

#### 14. Define supervisor mode. (remembering)

The ARM processor supports a protected supervisor mode. The protection mechanism ensures that user code cannot gain supervisor privileges without appropriate checks being carried out to ensure that the code is not attempting illegal operations. These functions generally include any accesses to hardware peripheral registers, and to widely used operations such as character input and output.

## 15. List the features of ARM instruction set. (remembering)

The most notable features of the ARM instruction set are:

- •The load-store architecture;

- •3-address data processing

- •Conditional execution of every instruction;

- •load and store multiple register instructions;

- •Single instruction that executes in a single clock cycle;

- •Open instruction set extension through the coprocessor instruction set

•Highly dense 16-bit compressed representation of the instruction set in the Thumb architecture.

#### 16. How I/O systems are handled in ARM?(understanding)

The ARM handles I/O (input/output) peripherals (such as disk controllers, network interfaces, and so on) as memory-mapped devices with interrupt support. The internal registers in these devices appear as addressable locations within the ARM's memory map and may be read and written using the same (load-store) instructions as any other memory locations.

#### 17. Mention the development tools available for ARM. (remembering)

- •ARM C compiler.

- •ARM assembler.

- •The linker.

- •ARM symbolic debugger.

- •ARMulator..

#### 18. Define ARMulator. Give its various levels of accuracy. (remembering)

The ARMulator (ARM emulator) is a suite of programs that models the behavior of various ARM processor cores in software on a host system. It can operate at various levels of accuracy: Instruction-accurate modeling gives the exact behavior of the system state without regard to the precise timing characteristics of the processor. Cycle-accurate modeling gives the exact behavior of the processor on a cycle by- cycle basis, allowing the exact number of clock cycles that a program requires to be established. Timing-accurate modeling presents signals at the correct time within a cycle, allowing logic delays to be accounted for.

## **19.** Give the steps in exception handling. (remembering)

The current state is saved by copying the PC into rl4\_exc and the CPSR into SPSR\_exc (where exc stands for the exception type). The processor operating mode is changed to the appropriate exception mode. The PC is forced to a value between 0016 and 1C16, the particular value depending on the type of exception.

## 20. Define Jump-start tools. (remembering)

The Jumpstart tools from VLSI Technology, Inc., include the same basic set of development tools but present a full X-windows interface on a suitable workstation rather than the command-line interface of the standard ARM toolkit. There are many other suppliers of tools that support ARM development.

## 21. What are the principal components in 3-stage pipelining? (remembering)

The principal components in 3-stage pipelining are:

- •The register bank

- •The barrel shifter

- •The ALU

- •The address register and incrementer

- •The data registers

- •The instruction decoder and associated control logic.

## 22. Define Thumb instruction set. (remembering)